为了方便各位同学交流学习,解决讨论问题,我们建立了一些微信群,作为互助交流的平台。

2.告知:姓名-课题组-研究方向,由编辑审核后邀请至对应交流群(生长,物性,器件);欢迎投稿欢迎课题组投递中文宣传稿,免费宣传成果,发布招聘广告,具体联系人:13162018291(微信同号)

成果介绍

在人工智能(AI)工作负载向边缘器件转移的推动下,对提供高密度、低功耗和可靠性的非易失性存储器解决方案的需求不断增长。然而,由于短沟道效应和单元电流限制,使用多晶硅(Poly-Si)沟道的3D NAND闪存在增加比特密度方面遇到了瓶颈。

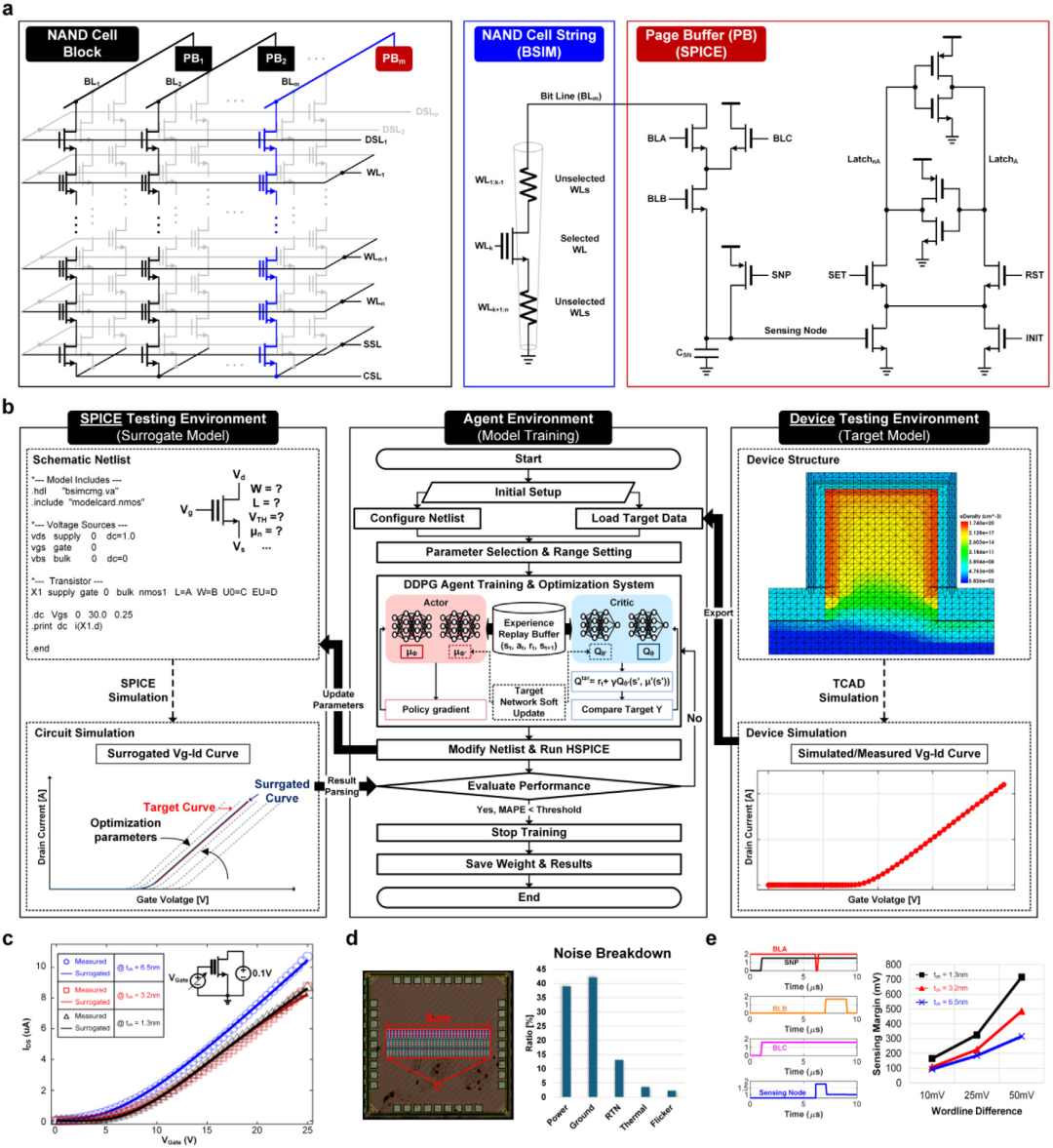

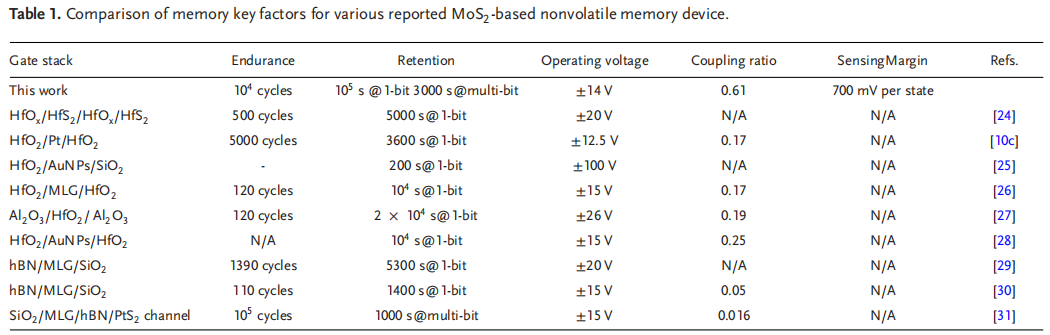

有鉴于此,近日,韩国庆北大学Byung Chul Jang和首尔市立大学Min-Jae Seo(共同通讯作者)等合作研究了MoS2作为3D NAND闪存单元的替代沟道材料。MoS2的低带隙有助于基于空穴注入的擦除,在中等电压下实现更宽的存储窗口。此外,采用低k(≈2.2)隧穿层提高了栅极耦合比,降低了编程/擦除电压,提高了可靠性,耐久时间可达104次,保持时间为105 s。综合分析,包括厚度相关的MoS2电学测量、温度相关的传导研究和技术计算机辅助设计(TCAD)模拟,阐明了沟道厚度与可靠性指标(如耐久性和保留性)之间的关系。此外,深度强化学习驱动的Berkeley短沟道IGFET模型(BSIM)参数校准使MoS2模型与制造的页面缓冲芯片无缝集成,允许电路级验证感知边界。该方法可应用于下一代存储器件的新沟道材料。这些结果表明,MoS2基非易失性存储器有效地满足了高密度、低功耗和可靠的存储需求,为以人工智能为中心的边缘计算提供了一个有前途的解决方案。

图文导读

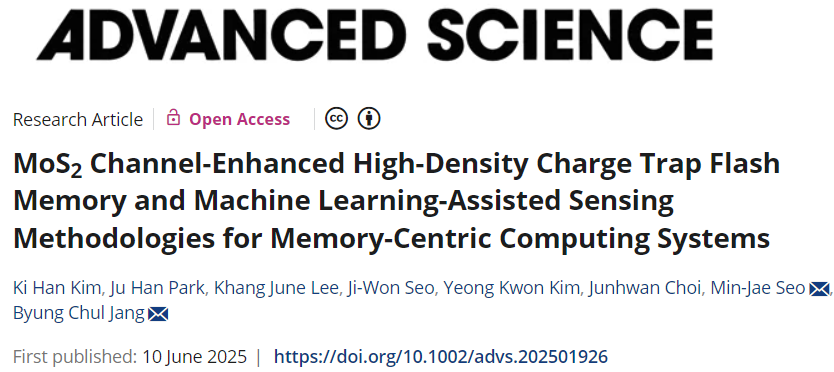

图1. (a)提高边缘器件系统性能的3D NAND闪存的示意图。(b)室温下各种块材和纳米材料基半导体的迁移率与带隙的关系综述。(c)不同厚度MoS2薄片的拉曼光谱。(d)沟道厚度分别为1.3、3.2和6.5 nm的MoS2基器件的电学特性。(e)MoS2基突触存储器件的示意图。(f)存储器件栅极堆叠的高分辨TEM横截面图像。(g)MoS2基存储器件在不同VGS

扫描范围下的电学特性。

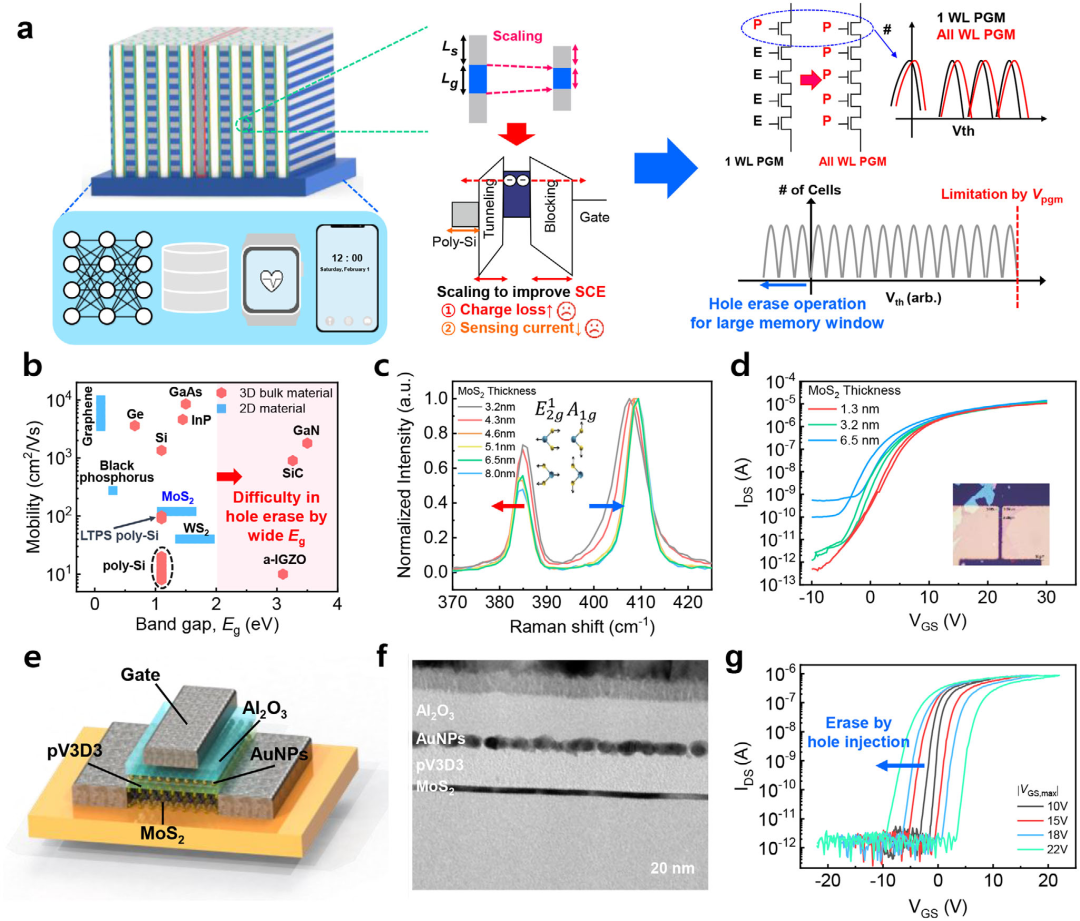

图2. (a)MoS2基器件与温度的关系。(b)低VDS下MoS2基器件沟道电阻的温度变化,以研究MoS2的传导机制。(c&d)对厚度分别为1.3 nm和6.5 nm的MoS2器件进行了校准后的TCAD仿真结果。(e&f)1.3 nm和6.5 nm厚度器件的MoS2沟道层在开关状态下模拟的电场分布。(g&h)1.3 nm和6.5 nm厚度器件在开关状态下模拟的MoS2沟道层的电子密度。

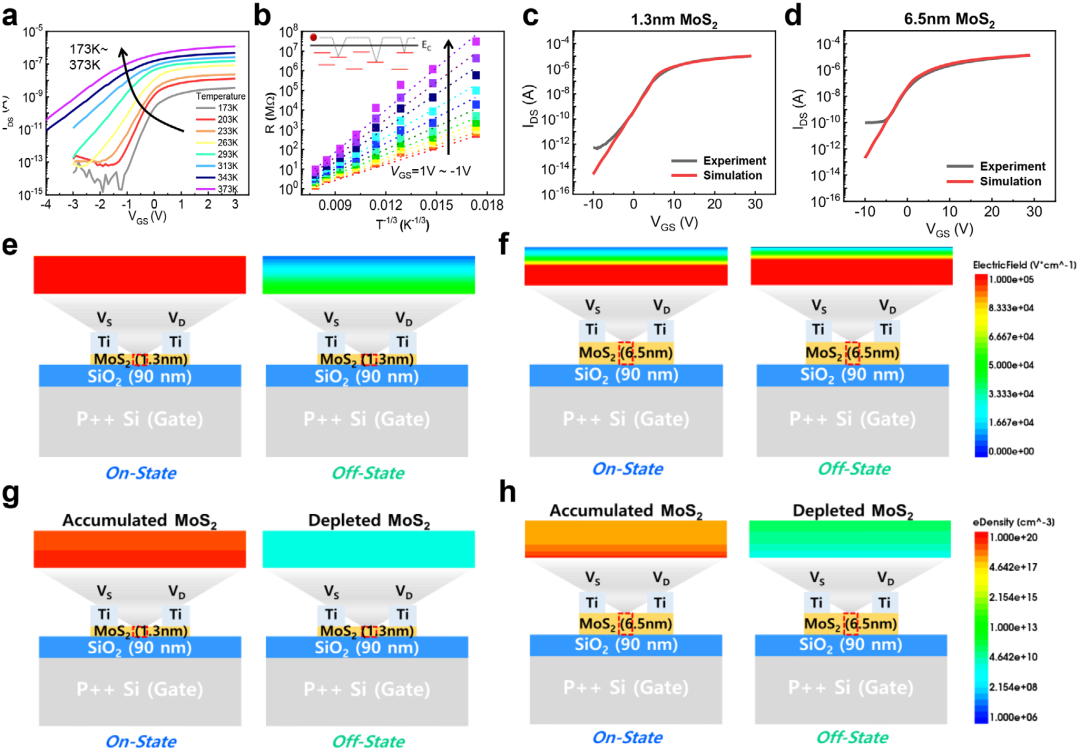

图3. (a)MoS2基存储器件的存储器窗口与沟道层数的关系。(b&c)不同沟道厚度的编程速度和擦除速度。(d)根据沟道厚度,基于初始VTh的存储器操作速度模型。(e)由于量子约束效应导致的薄沟道厚度带隙增加的能带图。

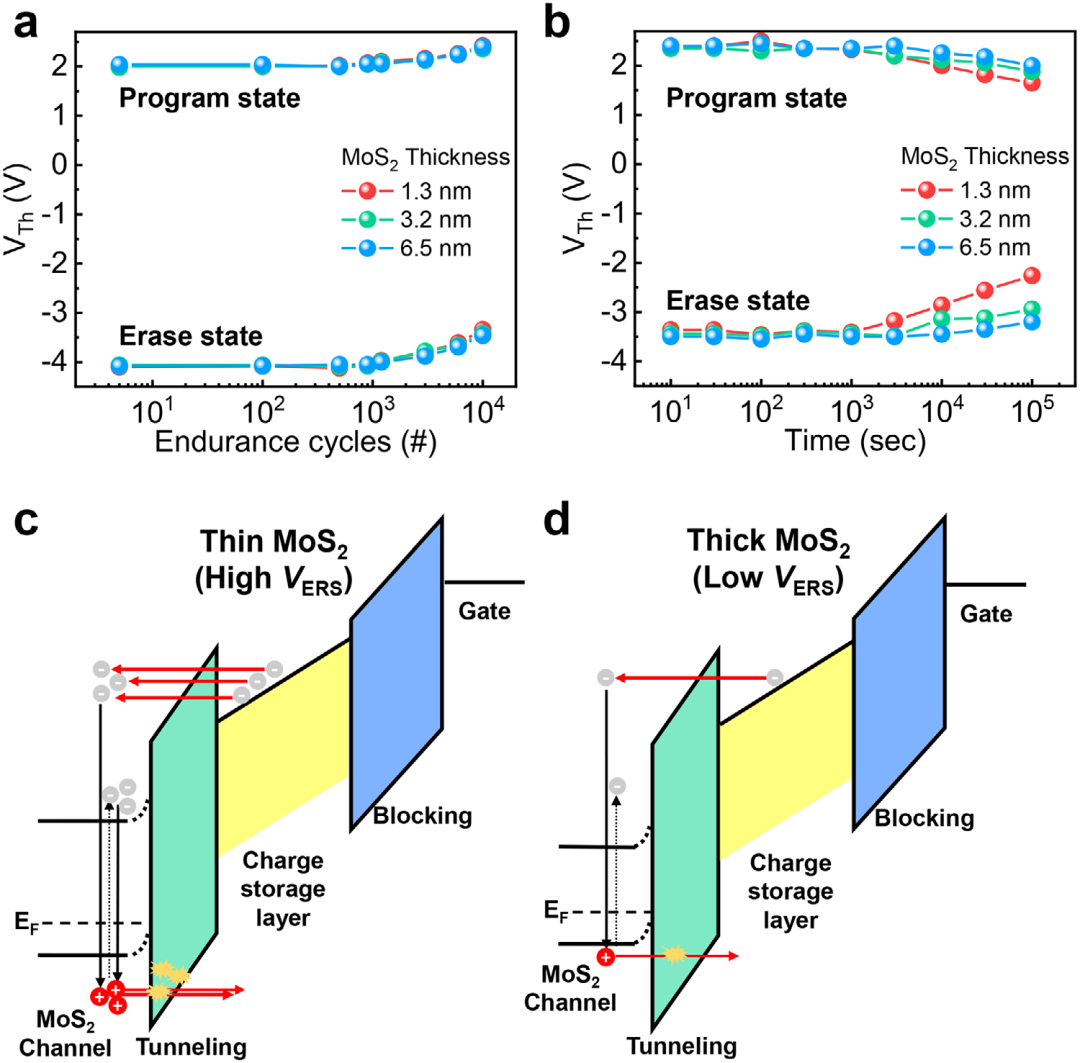

图4. (a)具有不同沟道厚度的MoS2存储器件的循环寿命。(b)具有不同沟道厚度的MoS2存储器件循环耐久性测试后的保留特性。(c&d)具有薄MoS2层和厚MoS2层的存储器件的AHI退化模型。

图5. (a)NAND Cell架构的框图。(b)提出的基于深度强化学习的BSIM模型代理框架流程图。(c)目标模型与替代模型的转移特性对比分析。(d)Die显微图像和系统噪声分解。(e)综合验证环境下不同字线电压差下的感知容限评估。

文献信息

MoS

2 Channel-Enhanced High-Density Charge Trap Flash Memory and Machine Learning-Assisted Sensing Methodologies for Memory-Centric Computing Systems

(Adv. Sci., 2025, DOI:0.1002/advs.202501926)

文献链接:https://advanced.onlinelibrary.wiley.com/doi/10.1002/advs.202501926

上海昂维科技有限公司现提供二维

材料单晶和薄膜等耗材,器件和光刻掩膜版定制

等微纳加工服务,以及各种测试分析,欢迎各位老师和同学咨询,竭诚

做好每一份服务。