1、【专利解密】三星半导体方案实现SRAM器件高可靠性运行及微缩化

2、上海市知识产权局:酌情延长专利、商标、集成电路布图设计事务办理相关期限

3、AMD直连型机器学习加速器专利曝光 垂直堆叠芯片I/O连接方案成焦点

1、【专利解密】三星半导体方案实现SRAM器件高可靠性运行及微缩化

【嘉勤点评】三星发明的半导体器件方案,能够改善连接栅电极、源极和漏极区的节点接触结构,并进一步改善静态随机存取存储器(SRAM)器件的工作特性和可靠性,从而有利于提高半导体器件的密度。

集微网消息,微缩技术可以用于提高半导体器件的密度,并逐渐发展了各式各样的多栅极晶体管,这种晶体管通常具有鳍形状和纳米线形状的多沟道有源图案,图案形成于芯片衬底上,在有源图案上还设置有栅极结构。

由于这种多栅极晶体管利用三维沟道来实现,因此比较容易进行微缩。此外,即使不增加多栅极晶体管的栅极长度也可以提高电流控制能力,并可以有效地抑制沟道区的电势受漏极电压影响的短沟道效应(SCE)。

而随着目前2~3nm芯片技术的深入研究以及半导体器件的节距尺寸减小,需要确保半导体器件中的接触之间的电容减小和电稳定性。为此,三星在2021年7月6日申请了一项名为“半导体器件”的发明专利(申请号:202110761662.0),申请人为三星电子株式会社。

根据该专利目前公开的相关资料,让我们一起来看看这项方案吧。

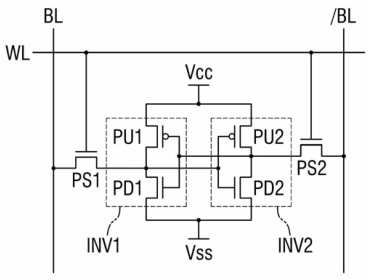

如上图,为该专利中发明的半导体器件的电路示意图,该半导体包括并联连接在电源节点Vcc和接地节点Vss之间的一对反相器INV1和INV2,以及连接到两个反相器中的每一者的输出节点的第一传输晶体管PS1和第二传输晶体管PS2。

第一反相器包括串联连接在电源节点与接地节点之间的第一上拉晶体管PU1和第一下拉晶体管PD1。同时,第二反相器包括串联连接在电源节点与接地节点之间的第二上拉晶体管PU2和第二下拉晶体管PD2。这两种上拉晶体管均为P型晶体管,下拉晶体管为N型晶体管。

而且,为了使第一反相器和第二反相器形成单个锁存电路,第一反相器的输入节点连接到第二反相器的输出节点,并且第二反相器的输入节点连接到第一反相器的输出节点,在上图中以SRAM单元的存储单元用作示意。

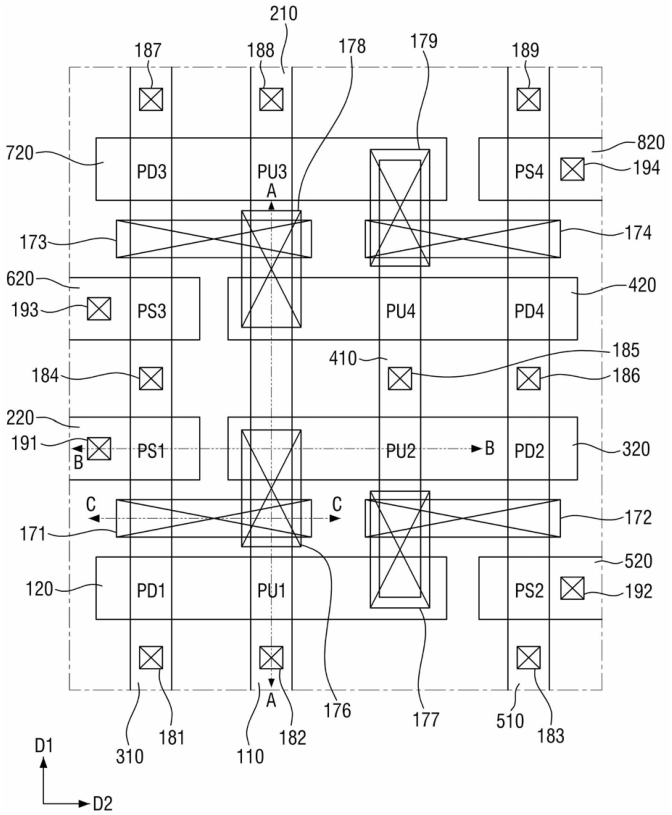

如上图,为上述半导体器件的放大布局图,在该结构中:110、210、310、410和510为有源图案;120、220、320、420、520、620、720和820为栅电极;171、172、173和174为桥接部件;176、177、178和179为节点部件;181、182、183、184、185、186、187、188和189为源极和漏极部件,以及191、192、193和194为栅极部件。

有源图案设置在SRAM区域中,第一有源图案110、第二有源图案210和第四有源图案410设置在SRAM的PMOS区域中,第三有源图案310和第五有源图案510设置在SRAM的NMOS区域中。这些有源图案均从各自的第一方向D1上纵长地延伸。

在衬底上还铺设有场绝缘膜105,其通常形成于上述有源图案的侧壁上,且突出到场绝缘膜上表面的上方,可以用例如等离子体增强化学气相沉积(PECVD)工艺和低压化学气相沉积(LPCVD)工艺的化学气相沉积(CVD)工艺来形成。

在上述第二层间绝缘膜196中设置有布线团200,其也在第一方向D1上纵长地延伸。布线图案不使用通路结构连接到第二源极上,从而可以减少从第一外延图案到布线图案的高度。且由于到布线图案的高度减小,因此晶体管的源极和漏极区与布线图案之间的电阻也可以减小,从而能够提高半导体器件的工作性能和可靠性。

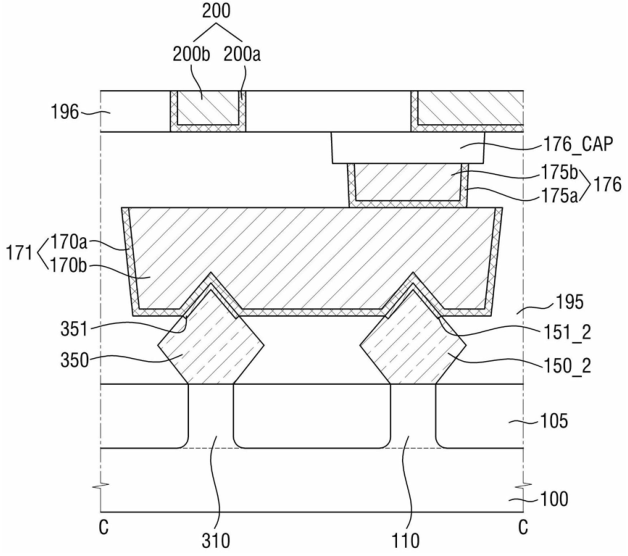

如上图,为半导体器件的截面示意图,在该半导体结构中,第一节点覆盖图案的下表面176b_CAP在第一方向D1上的宽度大于第一节点接触的上表面176us在第一方向D1上的宽度。此外,第一节点覆盖图案的下表面在第二方向D2上的宽度大于第一节点接触的上表面在第二方向D2上的宽度。

以上就是三星发明的半导体器件方案,这种半导体器件能够改善连接栅电极、源极和漏极区的节点接触结构,进一步改善静态随机存取存储器(SRAM)器件的工作特性和可靠性,从而有利于提高半导体器件的密度。

关于嘉勤

深圳市嘉勤知识产权代理有限公司由曾在华为等世界500强企业工作多年的知识产权专家、律师、专利代理人组成,熟悉中欧美知识产权法律理论和实务,在全球知识产权申请、布局、诉讼、许可谈判、交易、运营、标准专利协同创造、专利池建设、展会知识产权、跨境电商知识产权、知识产权海关保护等方面拥有丰富的经验。

(校对/holly)

2、上海市知识产权局:酌情延长专利、商标、集成电路布图设计事务办理相关期限

集微网消息,4月6日,上海市知识产权局印发《全力抗疫情助企业促发展的若干知识产权工作措施》,在“发挥知识产权助力疫情防控重要作用、提升知识产权金融服务能力、帮助困难企业恢复发展、加强知识产权服务保障”等方面提出11条具体措施。

其中包括:充分发挥知识产权融资作用。鼓励商业银行充分用好知识产权质押贷款贴息、风险补偿、优化不良率考核等扶持监管政策,放宽普惠型小微企业不良贷款容忍度,加快办理中小企业知识产权质押融资贷款审核手续,进一步增加小微企业首贷、质押增信贷款、无还本续贷,缓解中小微企业因疫情带来的资金压力。对商业银行按照2022年第二季度专利商标质押融资贷款工作绩效予以专项奖补。

加强知识产权保险服务。鼓励保险机构加大知识产权质押融资保证保险、知识产权执行保险等险种推广力度,简化知识产权保险理赔服务流程,提升知识产权保险服务便利化水平。

促进知识产权金融供需精准对接。依托市知识产权金融服务联盟开展中小微企业知识产权质押融资需求调查,及时公布商业银行、担保机构、保险公司等金融机构相关知识产权质押融资、担保、保险等产品服务信息。

酌情延长专利、商标、集成电路布图设计事务办理相关期限。对申请办理专利、商标、集成电路布图设计等事务,确因疫情相关原因延误相关期限,导致权利丧失的,协助按规定办理相关权利恢复手续。

(校对/小如)

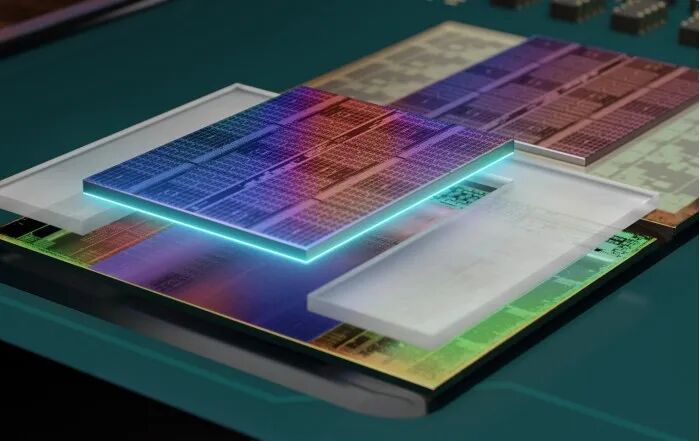

3、AMD直连型机器学习加速器专利曝光 垂直堆叠芯片I/O连接方案成焦点

2020 年 9 月 25 日,AMD 介绍了一项独特的处理器专利,特点是在 I/O 芯片上垂直堆叠了机器学习(ML)加速器。这意味着 AMD 可能正在准备基于数据中心的片上系统(SoC),并在其中整合现场可编辑门阵列(FPGA)或专用的 GPU 加速器。此前,该公司已在锐龙 R7-5800X3D 桌面处理器上尝试过 3D V-Cache,但这项技术可能很快推广到其它领域。

虽然除了 3D 堆叠缓存之外,我们不大可能在消费级市场上看到整合其它类型加速器的 AMD SoC 。

但由《直连型机器学习加速器》的专利描述可知,该技术主要由一个 FGPA 或计算 GPU 组成,用于处理堆叠在专用加速器相连的 IO 小芯片上的机器学习工作负载。

通常情况下,机器学习工作多在数据中心开展。而 AMD 的新技术,有望极大地加速运算,而无需在硬件系统中结合使用昂贵的定制芯片,其它优势还包括更高的能源效率、传输速率、以及丰富的功能扩展。

当然,AMD 在一年半前宣布收购 Xilinx 的时候,就已经有人猜到了这一天。由 3 月下旬公布的信息可知,这项新专利的署名人为 AMD 研究员 Maxim V. Kazakov 。如果进展顺利,我们或于 2023 年见到相关产品。

目前 AMD 正在开发代号为 Genoa 和 Bergamo 的霄龙(EPYC)服务器处理器,推测该公司很可能在 EPYC 产品线上,尝试集成机器学习加速器的 AI 处理器设计。

考虑到 Genoa 和 Bergamo 处理器的使用场景,整合垂直堆叠的 ML 加速器,确实有助于提升性能与功能体验。但随之而来的,很可能是功率的暴涨。

据说该公司的第五代 EPYC Turin 产品线具备 600W 的可配置热设计功耗(cTDP),直接较当前的 EPYC 7003 Milan CPU 翻番,且 SP5 新平台可提供 700W 的瞬时峰值功率。

此外基于已公开的文本内容,AMD 还给自己留下了相当大的灵活变通的空间。比如通用 / 专用处理器、常规的 CPU / GPU / ML 处理器、DSP / ASIC / FPGA,以及其它类型的集成电路(IC)。

更重要的是,AMD 可借助处理器后的硬件描述语言(HDL)指令和 netlists 等中间数据来制造,而这些指令集能够存储在可被计算机读取的介质上。

相信在 Xilinx 技术的加持下,AMD 最终可提供以计算为中心的 CPU、强大的 FPGA 设计、Pensando 可编程处理器系列、以及可靠的 x86 微架构。

至于多芯片设计,AMD 已经在 Infinity Fabric 互联技术上相当精进。对于企业客户来说,垂直堆叠技术还可为数据中心处理器带来更丰富的选项。

比如将面向数据中心的多瓦片 APU 和基于台积电 N4X 性能节点制造的处理器拼接到一起,并借助 GPU / FPGA 加速器、以及优化的增强型 N3E 工艺技术来进一步完善。

综上所述,AMD 将在未来产品线中更普遍地整合加速器,通过站在行业风口的最前沿,为数据中心客户提供更加多样化的产品组合。

更多新闻请点击进入爱集微小程序 阅读

1. 微软称改变Windows 11中任务栏位置这一功能并不重要

2. 上海崇明气膜实验室投用 可满足全区60万人口全员核酸检测

3. 私人宇航员对地分享SpaceX飞船以17000英里/小时飞行的旅程感受

4. 马斯克称人类最终可将意识移植到机器人上 曾称长生不老不利于社会

5. 乌克兰军队通过被抢劫的苹果AirPods定位与分析俄罗斯军队的行踪

6. Stellantis介绍规格大幅提升的Jeep Magneto 2.0电动概念越野车

7. 特斯拉得州工厂开业活动盛大,最终为的是招人

8. “全程参与中国制造业全球化和转型升级进程” 李东生入选《财富》“2022年中国最具影响力的50位商界领袖”

9. IMF:加密货币在腐败国家更受欢迎 应加强监管

10. 京东:1300多个仓库组织货源保障物资 供应链各环节逐步畅通